# AND8299/D

# EMC Tests and PCB Guidelines for Automotive Linear Regulators

Prepared by: David Apriletti ON Semiconductor

#### Introduction

Electromagnetic compatibility (EMC) is important for the functionality and security of electronic devices. Today's designers must deal with steadily increasing system frequencies, changing power limits, high-density layouts required by more complex systems, and the ever-present need for low manufacturing cost. Therefore, it is necessary to optimize EMC.

Linear regulators supply several types of loads including microcontrollers, one of the key devices in automotive applications.

This document concentrates on EMC for automotive basic knowledge, test methods at the IC level and ON Semiconductor standards. PCB guide lines are included to prevent any board effect or external coupling.

#### **Definition of EMC**

Electromagnetic compatibility (EMC) is the capacity of a piece of equipment to work properly in its normal environment, and not create electrical disturbances that would interfere with other equipment.

Electromagnetic susceptibility (EMS) is the level of resistance to electrical disturbances such as electromagnetic fields and conducted electrical noise.

Electromagnetic interference (EMI) is the level of conducted/radiated electrical noise created by the equipment.

Standards are addressing EMS or EMI issues for every type of application area.

These standards apply to finished equipment.

EMC tests must be performed on the sub-systems in order to evaluate and optimize applications for EMC performances. Standards for IC-level EMC testing have existed since 2003. Two Standards are commonly used: *IEC62132-4 (Direct Power Injection or DPI)* for EMS and the *IEC61967-4 (1 \Omega/150 \Omega method)*

## **Definition of Noise**

Susceptibility to radio frequency interference is becoming a major concern for integrated circuits, with the propagation of new and powerful electromagnetic sources. Electrostatic discharges, mains transients, switching of high currents and voltages or radio frequency (RF) generators are just some of the causes of electromagnetic interference. EMI can be

**ON Semiconductor®**

http://onsemi.com

transferred by electromagnetic waves, conduction, and inductive/capacitive coupling.

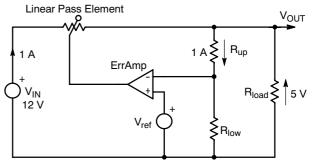

#### The Linear Regulators Architecture

The linear approach is often considered for low output noise generation.

Figure 1. Linear Power Supply

However, efficiency is one of the limitations of the linear approach.

Intrinsically, linear regulators do not generate noise and EMC disturbances, but they can be susceptible to noise generated by other components like microcontrollers, SMPS, and logic circuits.

According to the IEC standards, Linear regulators are tested using the Direct Power Injection method (IEC62132-4).

#### **Direct Power Injection**

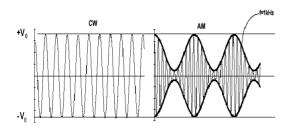

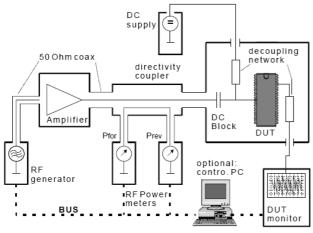

The RF disturbance (a sinusoidal waveform from 150 kHz to 1 GHz CW (continuous wave) or AM (Amplitude modulation, 1 KHZ, 80%) is injected on the component pin under test through a decoupling block as shown on Figure 2. The DC block is realized by a capacitor. The RF disturbance is monitored through the directional coupler by measuring the forward power and the reflected power.

The continuous wave means the successive oscillations are identical under steady state conditions. The amplitude modulation (AM) is the process by which a continuous high frequency wave is caused to vary in amplitude by the action of another wave containing information. The basic requirement when an amplitude modulation is applied is the peak power shall have the same value as the peak power when a continuous wave is applied, regardless the modulation index m.

$$P_{AM-Peak} = P_{CW-Peak}$$

and

$$P_{AM} = P_{CW} \frac{2 + m^2}{2(1 + m)^2}$$

For example, 80% Amplitude Modulation, 1 KHz (m = 0.8) result is

$$P_{AM} = 0.407 \cdot P_{CW}$$

The forward power is the amount of power that is sent from the RF source towards the DUT without considering the RF power that is being reflected backwards by the DUT.

To reduce the reflection effects, the set up is built with 50  $\Omega$  cable and 50  $\Omega$  adapted printed circuit board tracks, so that the injection path is 50  $\Omega$  almost all the way from the RF generator to the DUT. However, the DUT impedance is strongly dependant on frequency, therefore creating reflections and resonant effects. An attenuator (3 dB) is inserted just before the capacitor to avoid errors due to cable effects.

Figure 2. DPI Set up

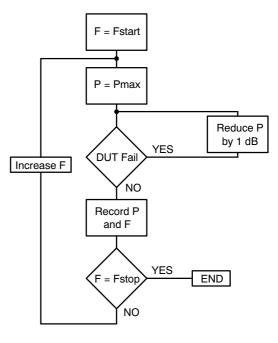

The following algorithm is used to test components with the DPI method.

**Figure 3. DPI Flowchart**

For each frequency step, power is set to the specified power limit. If the device fails, the power is decreased in 1 dBm steps until the DUT exhibits correct performance.

#### Linear Regulators Tested with DPI Method

The usual limit is 1 W (30 dBm, Forward power CW) for global pins and 17 dBm, Forward power CW for local pins. A global pin carries a signal or power which enters or leaves the application board. A local pin carries a signal or power which does not leave the application board. It remains on the application board as a signal between two components. For linear regulators, the Input and Output pins are considered as global pins and are tested at the 30 dBm compliance limit. Some linear regulators have added features, such as Reset and Delay circuitry. In this case, associated pins are considered as local pins and tested to the 17 dBm compliance limit.

The usual failure condition is the Output voltage. For linear regulators with additional features, other pins are monitored and must maintain their correct state (logic pins).

| Method: DPI according to IEC 62132-4                                                                              |

|-------------------------------------------------------------------------------------------------------------------|

| Frequency range: 1MHz to 1GHz                                                                                     |

| Frequency increment: 5%                                                                                           |

| Increment duration: 1 s                                                                                           |

| Frequency modulation: None (continuous wave)                                                                      |

| RF Calibration method: Substitution                                                                               |

| Power compliance limit: 33dBm for global pin<br>17dBm for local pin                                               |

| Powerstepsize: 1dBm                                                                                               |

| Device pins injected: MN; RESET, VOUT                                                                             |

| Device pins monitored: VOUT; RESET                                                                                |

| Load resistance: 100 ohm s                                                                                        |

| DC input voltage: 12V                                                                                             |

| Acceptance criteria:<br>Output voltage within 4% of nominal value<br>Digital outputs remain in correct state +-1V |

**Figure 4. Typical Test Conditions**

# General Golden Rules for PCB

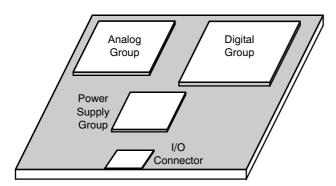

All components should be placed with an appropriate functional group and their tracks routed within their designated PCB area. A recommended arrangement of functional groups on PCB is shown in Figure 8.

Figure 5. Arrangement of Functional Groups on PCB

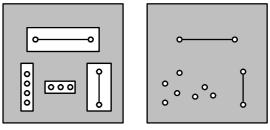

Place ground plane(s) under all components and all their associated tracks. A continuous ground plane with no avoidance is recommended.

- A good ground plane is achieved by using a complete layer for ground

- Do not cut the ground plane by routing signal lines in GND plane.

- Provide a length / width ratio less than 5 for the PCB. (At a ratio > 5 the inductance of the ground plane increases.)

Figure 6. Maximizing Ground on PCB

# **Connection to Ground**

- Connect each component directly to plane.

- Use a via for each component-pin for GND-connection instead of GND-traces.

- Connections to ground must be shorter than 0.5 mm (20 mils).

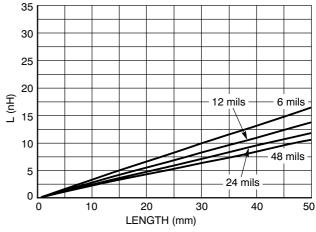

Figure 7. Inductance and Capacitance Values of a Strip Line Above a Ground Plane

Trace widths should be around 20 mils to reduce partial parasitic inductance.

Figure 8. Effect of the Trace's Width on Parasitic Inductance

### **Particular Linear Regulator Guidelines**

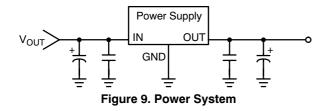

Power supplies should be located as close to the power entry point to the PCB, and as close as possible to powered circuitry. Closely routed tracks (to minimize the area between conductors, and hence the inductance) should be used to connect the power source to the local power distribution system.

Power feeds should always be decoupled at their entry points onto the PCB.

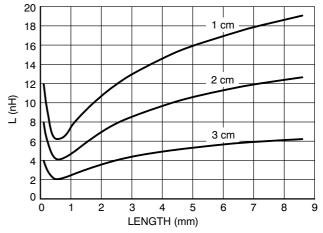

Bulk capacitors should always be parallel decoupled with one or more lower valued high frequency capacitors with low ESL (equivalent series inductance). Place the smallest value decoupling capacitor closest to a device to be decoupled.

High-frequency, low-inductance ceramic capacitors should be used for IC decoupling at each power pin. Use 0.1  $\mu$ F for up to 15 MHz, and 0.01  $\mu$ F over 15 MHz. The decoupling capacitor should be located as close as physically possible to the IC's power pin.

Printed circuit board traces which carry high switching current with fast rise/fall times (5 – 10 ns) should maintain at least 3 mm spacing from other signal traces which run parallel to them, and/or ground guard traces should be placed between them.

Corresponding power and ground signals should always be routed in parallel to minimize loop area thus reducing loop impedance (Figure 10).

Figure 10. PS Routing

### Layout Example

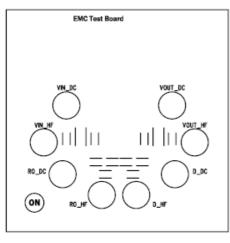

Two boards have been made. The first one follows the EMC design guidelines listed above. The second one is a typical applications board without consideration of EMC rules. A linear regulator with reset function has been tested with the DPI method.

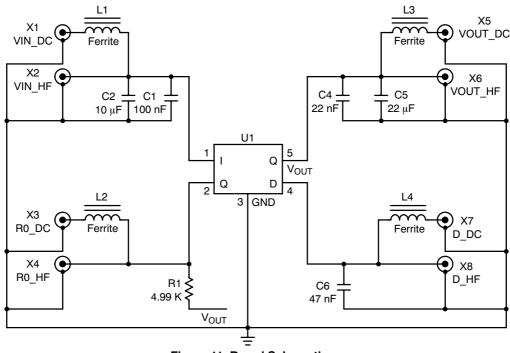

Figure 11. Board Schematic

The board schematic includes tantalum capacitors on the input and output. Two small ceramic capacitors have been added.

Figure 4 shows the failure criteria used for this example. 4% variation for the output voltage and 2 V for the reset considered as a logic output pin are considered acceptable.

# Good EMC Test Board

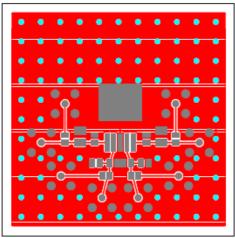

Figure 12. Assembly Top Good Layout

Figure 13. Top Layer EMC Layout

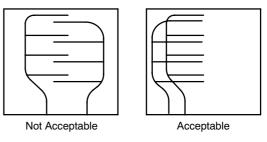

20 mils trace widths are used with short connections. Input and output capacitors are located as close as possible to the DUT pin. It is a four layer board with ground plane.

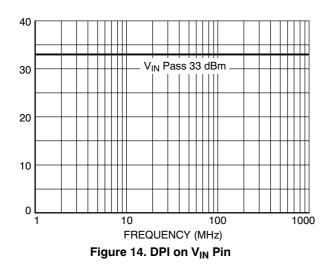

The Device passes 33 dBm injection on  $V_{\rm IN}$  pin with Reset and  $V_{\rm OUT}$  pins monitored.

# PCB Without Consideration of EMC Rules

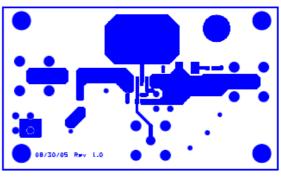

The second PCB is a demo board. The same components are used with a different layout.

Figure 15. Top Layer Typ Layout

The demo board is a two layer board with ground plane. The trace widths are bigger than 20 mils which increases parasitic inductance. The distance from capacitor to the DUT pins is more than 1 cm. The layout does not follow the power supply guide lines.

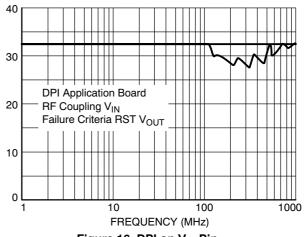

Figure 16. DPI on  $V_{IN}$  Pin

## AND8299/D

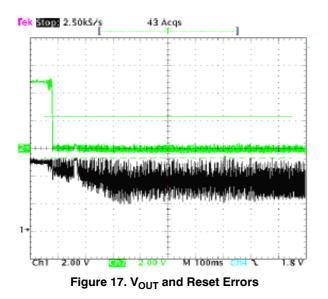

In the same test condition, the device is not compliant with 33 dBm power limit in the whole frequency range. Issues appear between 100 MHz and 1 GHz. The lower limit is around 25 dBm @ 205 MHz The RF signal perturbed the output signal and created a reset.

33 dBm is 2 W injection; 25 dBm is 0.3 W injection which is a large performance difference for the same bill of materials.

#### Conclusion

As started in the introduction, EMC takes into account Susceptibility and Emission of the components. Due to the PCB connections, the coupling paths have to be considered such as another way for EMC improvement at system level.

Obviously, EMI must reach the traces in order to disturb the components. This means that the loops, long length and large surface of the conductors are vulnerable to EMI, making the PCB the principal subject of EMC improvements.

Following EMC rules will reduce design costs and time-to-market, while improving reliability and performance of the design.

#### REFERENCES

[1] S Ben Dhia, M Ramdani, E Sicard, *"Electromagnetic Compatibility of Integrated Circuits"*, Spinger 2006

[2] A. E. Ruehli, "Inductance calculation on a complex integrated circuit environment", IBM Journal, 1972, p470-481.

[3] M Gondon "Parasitics elements associated to the printed circuits board tracks", On Semiconductor 2006

[4] IEC 62132, 2003, "*Characterization of integrated circuits electromagnetic immunity*", IEC standard; www.iec.ch

[5] M Montrose, "Printed Circuit Board Design Techniques for EMC Compliance", 1996 IEEE Press

ON Semiconductor and use registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product core uses SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use personal and source of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5773-3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative